## **TDA6101Q**

#### **FEATURES**

- High bandwidth and high slew rate

- No external heatsink required

- Black-current measurement output for Automatic Black-current Stabilization (ABS)

- Two cathode outputs; one for DC currents, and one for transient currents

- A feedback output separated from the cathode outputs

- Internal protection against positive appearing Cathode-Ray Tube (CRT) flashover discharges

- ESD protection

- Simple application with a variety of colour decoders

- Differential input with a designed maximum common mode input capacitance of 3 pF, a maximum differential mode input capacitance of 0.5 pF and a differential input voltage temperature drift of 20 μV/K

- · Defined switch-off behaviour.

#### **GENERAL DESCRIPTION**

The TDA6101Q is a video output amplifier with 9 MHz bandwidth. The device is contained in a single in-line 9-pin medium power (DBS9MPF) package, using high-voltage DMOS technology, intended to drive the cathode of a colour CRT.

### **QUICK REFERENCE DATA**

| SYMBOL                            | PARAMETER                             | CONDITIONS            | MIN.      | TYP. | MAX.      | UNIT |

|-----------------------------------|---------------------------------------|-----------------------|-----------|------|-----------|------|

| $V_{DDH}$                         | high level supply voltage             |                       | 0         | _    | 250       | V    |

| $V_{DDL}$                         | low level supply voltage              |                       | 0         | _    | 14        | V    |

| I <sub>DDH</sub>                  | quiescent high voltage supply current | $V_{oc} = 0.5V_{DDH}$ | 3.5       | 4.4  | 5.5       | mA   |

| I <sub>DDL</sub>                  | quiescent low voltage supply current  | $V_{oc} = 0.5V_{DDH}$ | 2.2       | 2.8  | 3.5       | mA   |

| VI                                | input voltage                         |                       | 0         | -    | $V_{DDL}$ | V    |

| V <sub>oc</sub> , V <sub>fb</sub> | output voltage                        |                       | $V_{DDL}$ | -    | $V_{DDH}$ | V    |

| T <sub>stg</sub>                  | storage temperature                   |                       | -55       | -    | +150      | °C   |

| T <sub>amb</sub>                  | operating ambient temperature         |                       | -20       | _    | +65       | °C   |

### **ORDERING INFORMATION**

| TYPE NUMBER   |         | PACKAGE                                                     |          |  |  |

|---------------|---------|-------------------------------------------------------------|----------|--|--|

| I TPE NOWIDER | NAME    | DESCRIPTION                                                 | VERSION  |  |  |

| TDA6101Q      | DBS9MPF | plastic DIL-bent-SIL medium power package with fin; 9 leads | SOT111-1 |  |  |

2

## TDA6101Q

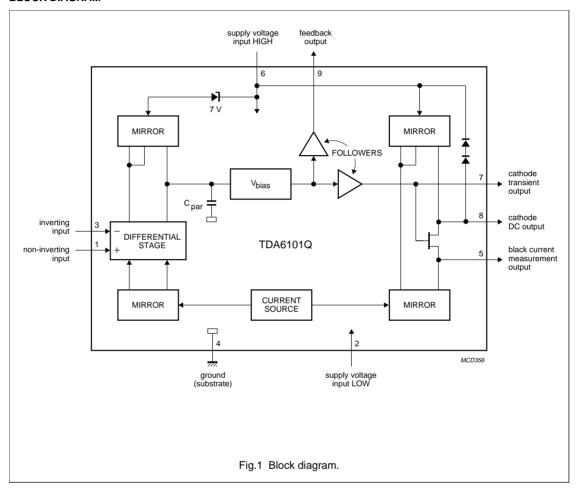

### **BLOCK DIAGRAM**

3

# TDA6101Q

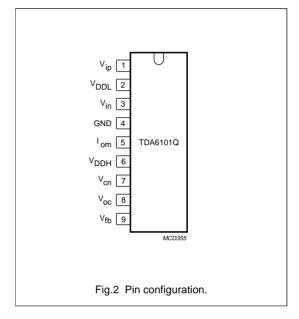

### **PINNING**

| SYMBOL           | PIN | DESCRIPTION                      |  |

|------------------|-----|----------------------------------|--|

| V <sub>ip</sub>  | 1   | non-inverting voltage input      |  |

| V <sub>DDL</sub> | 2   | supply voltage LOW               |  |

| V <sub>in</sub>  | 3   | inverting voltage input          |  |

| GND              | 4   | ground, substrate                |  |

| I <sub>om</sub>  | 5   | black current measurement output |  |

| $V_{DDH}$        | 6   | supply voltage HIGH              |  |

| V <sub>cn</sub>  | 7   | cathode transient voltage output |  |

| V <sub>oc</sub>  | 8   | cathode DC voltage output        |  |

| V <sub>fb</sub>  | 9   | feedback voltage output          |  |

TDA6101Q

### LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134). Voltages measured with respect to GND (pin 4); currents as specified in Fig.1; unless otherwise specified.

| SYMBOL                           | PARAMETER                                       | CONDITIONS                   | MIN.             | MAX.             | UNIT |

|----------------------------------|-------------------------------------------------|------------------------------|------------------|------------------|------|

| $V_{DDH}$                        | high level supply voltage                       |                              | 0                | 250              | V    |

| $V_{DDL}$                        | low level supply voltage                        |                              | 0                | 14               | V    |

| VI                               | input voltage                                   |                              | 0                | V <sub>DDL</sub> | V    |

| V <sub>Idm</sub>                 | differential mode input voltage                 |                              | -6               | +6               | V    |

| V <sub>om</sub>                  | measurement output voltage                      |                              | 0                | V <sub>DDL</sub> |      |

| V <sub>oc</sub>                  | cathode output voltage                          |                              | V <sub>DDL</sub> | $V_{DDH}$        | V    |

| V <sub>fb</sub>                  | feedback output voltage                         |                              | V <sub>DDL</sub> | V <sub>DDH</sub> | V    |

| I <sub>in</sub> ,I <sub>ip</sub> | input current                                   |                              | 0                | 1                | mA   |

| I <sub>ocsmL</sub>               | low non-repetitive peak cathode output current  | flashover discharge = 100 μC | 0                | 5                | А    |

| I <sub>ocsmH</sub>               | high non-repetitive peak cathode output current | flashover discharge = 100 nC | 0                | 10               | А    |

| P <sub>tot</sub>                 | total power dissipation                         |                              | 0                | 1.9              | W    |

| T <sub>stg</sub>                 | storage temperature                             |                              | -55              | +150             | °C   |

| T <sub>j</sub>                   | junction temperature                            |                              | -20              | +150             | °C   |

| V <sub>es</sub>                  | electrostatic handling                          |                              |                  |                  |      |

|                                  | human body model (HBM)                          |                              | -                | > 1500           | V    |

|                                  | machine model (MM)                              |                              | -                | > 400            | V    |

### **HANDLING**

Inputs and outputs are protected against electrostatic discharge in normal handling. However, to be totally safe, it is desirable to take normal precautions appropriate to handling MOS devices (see "Handling MOS Devices").

### **QUALITY SPECIFICATION**

Quality specification "SNW-FQ-611 part E" is applicable, except for ESD Human body model see Chapter "Limiting values", and can be found in the "Quality reference handbook" (ordering number 9398 510 63011).

### THERMAL CHARACTERISTICS

| SYMBOL              | PARAMETER <sup>(1)</sup>                                | VALUE | UNIT |

|---------------------|---------------------------------------------------------|-------|------|

| R <sub>th j-a</sub> | thermal resistance from junction to ambient in free air | 56    | K/W  |

| R <sub>th j-c</sub> | thermal resistance from junction to case                | 12    | K/W  |

#### Note

1. External heatsink not required.

1995 Feb 07 5

TDA6101Q

### **CHARACTERISTICS**

Operating range:  $T_{amb}$  = -20 to 65 °C;  $V_{DDH}$  = 180 to 210 V;  $V_{DDL}$  = 10.8 to 13.2 V;  $V_{ip}$  = 2.6 to 5 V;

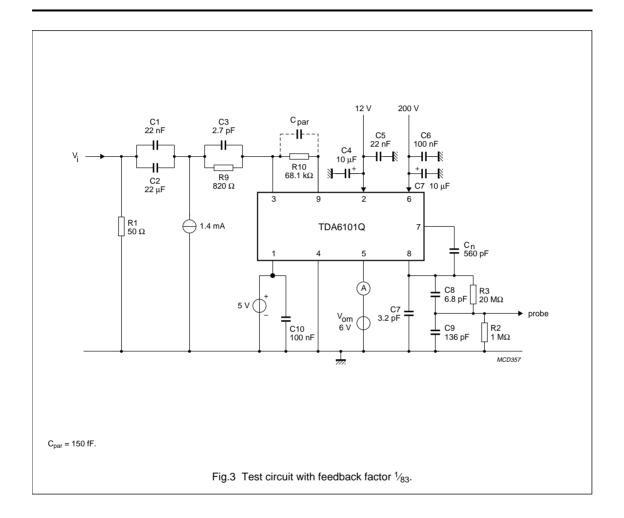

$V_{om} = 1.4 \text{ V to V}_{DDL}$ . Test conditions (unless otherwise specified):  $T_{amb} = 25 \text{ °C}$ ;  $V_{DDH} = 200 \text{ V}$ ;  $V_{DDL} = 12 \text{ V}$ ;  $V_{ip} = 5 \text{ V}$ ;  $V_{om} = 6 \text{ V}$ ;  $C_{L} = 10 \text{ pF}$  ( $C_{L}$  consists of parasitic and cathode capacitance); measured in test circuit Fig.3.

| SYMBOL                                              | PARAMETER                                                                      | CONDITIONS                                                                                                                                                                                                                           | MIN.                  | TYP. | MAX. | UNIT |

|-----------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|------|------|

| I <sub>DDH</sub>                                    | quiescent HIGH voltage supply current                                          | $V_{oc} = 0.5V_{DDH}$                                                                                                                                                                                                                | 3.5                   | 4.4  | 5.5  | mA   |

| I <sub>DDL</sub>                                    | quiescent LOW voltage supply current                                           | $V_{oc} = 0.5V_{DDH}$                                                                                                                                                                                                                | 2.2                   | 2.8  | 3.5  | mA   |

| I <sub>bias</sub>                                   | input bias current                                                             | $V_{oc} = 0.5V_{DDH}$                                                                                                                                                                                                                | 0                     | _    | 20   | μΑ   |

| I <sub>offset</sub>                                 | input offset current                                                           | $V_{oc} = 0.5V_{DDH}$                                                                                                                                                                                                                | -3                    | _    | +3   | μΑ   |

| I <sub>om(offset)</sub>                             | offset current of measurement output                                           | $I_{oc} = 0 \mu A;$<br>-1.0 V < V <sub>1-3</sub> < 1.0 V;<br>1.4 V < V <sub>om</sub> < V <sub>DDL</sub>                                                                                                                              | -5                    | 0    | +5   | μА   |

| $\frac{\Delta I_{\text{om}}}{\Delta I_{\text{oc}}}$ | linearity of current transfer                                                  | $-10 \ \mu A < I_{oc} < 3 \ mA;$<br>$-1.0 \ V < V_{1-3} < 1.0 \ V;$<br>$1.4 \ V < V_{om} < V_{DDL}$                                                                                                                                  | 0.9                   | 1.0  | 1.1  |      |

| V <sub>offset</sub>                                 | input offset voltage                                                           | $V_{oc} = 0.5V_{DDH}$                                                                                                                                                                                                                | -50                   | _    | +50  | mV   |

| V <sub>oc(min)</sub>                                | minimum output voltage                                                         | V <sub>1-3</sub> = -1 V                                                                                                                                                                                                              | _                     | _    | 20   | V    |

| V <sub>oc(max)</sub>                                | maximum output voltage                                                         | V <sub>1-3</sub> = -1 V                                                                                                                                                                                                              | V <sub>DDH</sub> – 12 | _    | _    | V    |

| GB                                                  | gain-bandwidth product of open-loop gain: V <sub>fb</sub> / V <sub>i, dm</sub> | f = 500 kHz; V <sub>ocDC</sub> = 100 V                                                                                                                                                                                               | _                     | 0.8  | -    | GHz  |

| B <sub>S</sub>                                      | small signal bandwidth                                                         | V <sub>ocAC</sub> = 60 V (p-p);<br>V <sub>ocDC</sub> = 100 V                                                                                                                                                                         | 7                     | 9    | -    | MHz  |

| B <sub>L</sub>                                      | large signal bandwidth                                                         | V <sub>ocAC</sub> = 100 V (p-p);<br>V <sub>ocDC</sub> = 100 V                                                                                                                                                                        | 5.5                   | 7    | -    | MHz  |

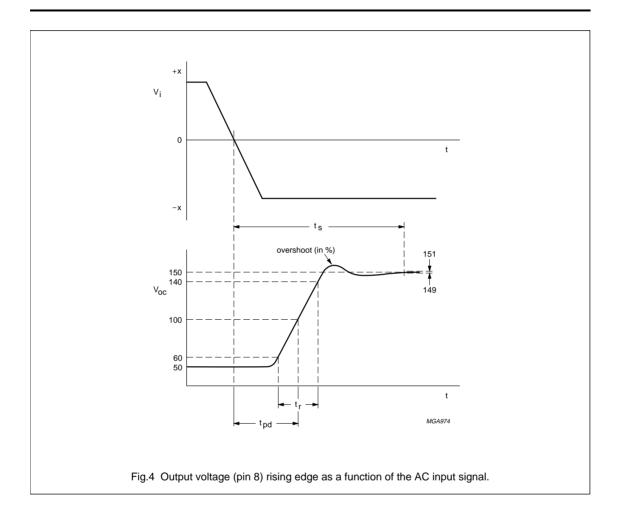

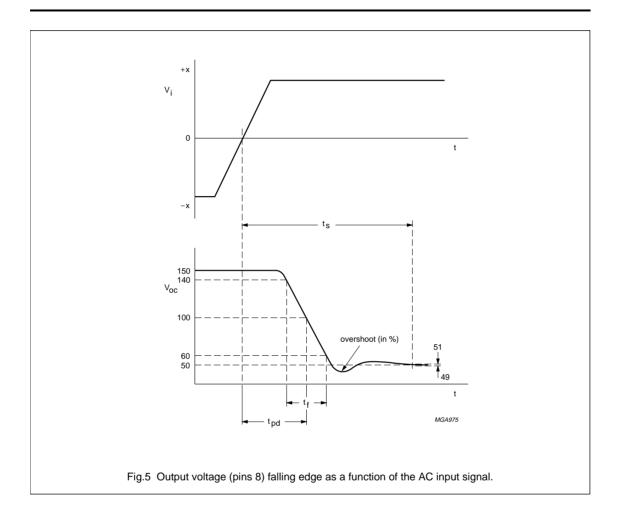

| t <sub>pd</sub>                                     | cathode output propagation delay time 50% input to 50% output                  | $\begin{aligned} &V_{\text{ocAC}} = 100 \text{ V (p-p);} \\ &V_{\text{ocDC}} = 100 \text{ V square} \\ &\text{wave; } f < 1 \text{ MHz;} \\ &t_{\text{r}} = t_{\text{f}} = 40 \text{ ns;} \\ &\text{see Figs 4 and 5} \end{aligned}$ | 27                    | 38   | 49   | ns   |

| t <sub>r</sub>                                      | cathode output rise time 10% output to 90% output                              | $V_{oc}$ = 50 to 150 V square<br>wave; f < 1 MHz; t <sub>f</sub> = 40 ns;<br>see Fig.4                                                                                                                                               | 43                    | 55   | 68   | ns   |

| t <sub>f</sub>                                      | cathode output fall time 90% output to 10% output                              | $V_{oc}$ = 150 to 50 V square<br>wave; f < 1 MHz; t <sub>r</sub> = 40 ns;<br>see Fig.5                                                                                                                                               | 43                    | 55   | 68   | ns   |

| t <sub>s</sub>                                      | settling time 50% input to (99% < output < 101%)                               | $V_{ocAC}$ = 100 V (p-p);<br>$V_{ocDC}$ = 100 V square<br>wave; f < 1 MHz;<br>$t_r$ = $t_f$ = 40 ns;<br>see Figs 4 and 5                                                                                                             | _                     | -    | 350  | ns   |

| SR                                                  | slew rate between 50 V to 150 V                                                | $V_{1-3} = 2 \text{ V (p-p)}$ square wave; f < 1 MHz; $t_r = t_f = 40 \text{ ns}$                                                                                                                                                    | -                     | 1700 | _    | V/μs |

## TDA6101Q

| SYMBOL         | PARAMETER                           | CONDITIONS                                                                                                                                                                                       | MIN. | TYP. | MAX. | UNIT |

|----------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| O <sub>v</sub> | cathode output voltage overshoot    | $\begin{split} &V_{ocAC} = 100 \text{ V (p-p);} \\ &V_{ocDC} = 100 \text{ V square} \\ &wave \text{ f < 1 MHz;} \\ &t_r = t_f = 40 \text{ ns;} \\ &see \text{ Figs 4 and 5; note 1} \end{split}$ | _    | 9    | _    | %    |

| SVRRH          | high supply voltage rejection ratio | f < 50 kHz; note 2                                                                                                                                                                               | _    | 85   | _    | dB   |

| SVRRL          | low supply voltage rejection ratio  | f < 50 kHz; note 2                                                                                                                                                                               | _    | 70   | _    | dB   |

#### Notes

- 1. If the difference between  $V_{DDL}$  and  $V_{ip}$  is less than 7 V, overshoot cannot be specified.

- 2. SVRR: The ratio of the change in supply voltage to the change in input voltage when there is no change in output voltage.

7

### Cathode output

The cathode output is protected against peak currents (caused by positive voltage peaks during high-resistance flash) of 5 A maximum with a charge content of 100  $\mu$ C.

The cathode is also protected against peak currents (caused by positive voltage peaks during low-resistance flash) of 10 A maximum with a charge content of 100 nC.

### Flashover protection

The TDA6101Q incorporates protection diodes against CRT flashover discharges that clamp the cathode output pin to the  $V_{DDH}$  pin. The DC supply voltage at the  $V_{DDH}$  pin has to be within the operating range of 180 to 210 V to ensure that the Absolute Maximum Rating for  $V_{DDH}$  of 250 V will not be exceeded during flashover. To limit the diode current, an external 820  $\Omega$  carbon high-voltage resistor in series with the cathode output and a 2 kV spark gap are needed (for this resistor-value, the CRT has to be connected to the main PCB). This addition produces an increase in the rise and fall times of approximately 5 ns and a decrease in the overshoot of approximately 3%.

V<sub>DDH</sub> to GND must be decoupled:

- With a capacitor >20 nF with good HF behaviour (e.g. foil). This capacitance must be placed as close as possible to pins 6 and 4, but definitely within 5 mm.

- 2. With a capacitor >10  $\mu$ F on the picture tube base print (common for three output stages).

V<sub>DDL</sub> to GND must be decoupled:

With a capacitor >20 nF with good HF behaviour (e.g. ceramic). This capacitance must be placed as close as possible to pins 2 and 4, but definitely within 10 mm.

#### Switch-off behaviour

The switch-off behaviour of the TDA6101Q is defined: when the bias current becomes zero, at  $V_{DDL}$  (pin 2) lower than approximately 5 V, all the output pins (pins 7, 8 and 9) will be high.

# TDA6101Q

8

# TDA6101Q

9

# TDA6101Q

1995 Feb 07 10

## TDA6101Q

### **TEST AND APPLICATION INFORMATION**

### Dissipation

Regarding dissipation, distinction must first be made between static dissipation (independent of frequency) and dynamic dissipation (proportional to frequency).

The static dissipation of the TDA6101Q is due to high and low voltage supply currents and load currents in the feedback network and CRT.

The static dissipation equals:

$$\begin{aligned} P_{stat} &= V_{DDL} \times I_{DDL} + V_{DDH} \times I_{DDH} \\ &+ V_{oc} \times I_{oc} - V_{fb} \times \left(\frac{V_{fb}}{R_{fb}}\right) \end{aligned}$$

R<sub>fb</sub> = value of feedback resistor.

$I_{oc} = DC$  value of cathode current.

The dynamic dissipation equals:

$$P_{dyn} = V_{DDH} \times (C_L + C_{fb} + C_{int}) \times f_i \times V_{o(p-p)} \times \delta$$

C<sub>L</sub> = load capacitance.

$C_{fb}$  = feedback capacitance ( $\approx$  150 fF).

C<sub>int</sub> = internal load capacitance (≈ 4 pF).

$f_i$  = input frequency.

$V_{o(p-p)}$  = output voltage (peak-to-peak value).

$\delta$  = non-blanking duty-cycle ( $\approx$  0.8).

The IC must be mounted on the picture tube base print to minimize the load capacitance  $(C_L)$ .